富士通在“Technology Update 2025”技术更新活动上披露了其全新 Arm 架构 Monaka 处理器的详细路线图,明确将 Monaka 系列定位为公司下一代关键数据中心 CPU 平台,首批产品计划于 2027 年量产,并采用 2 nm 制程工艺。

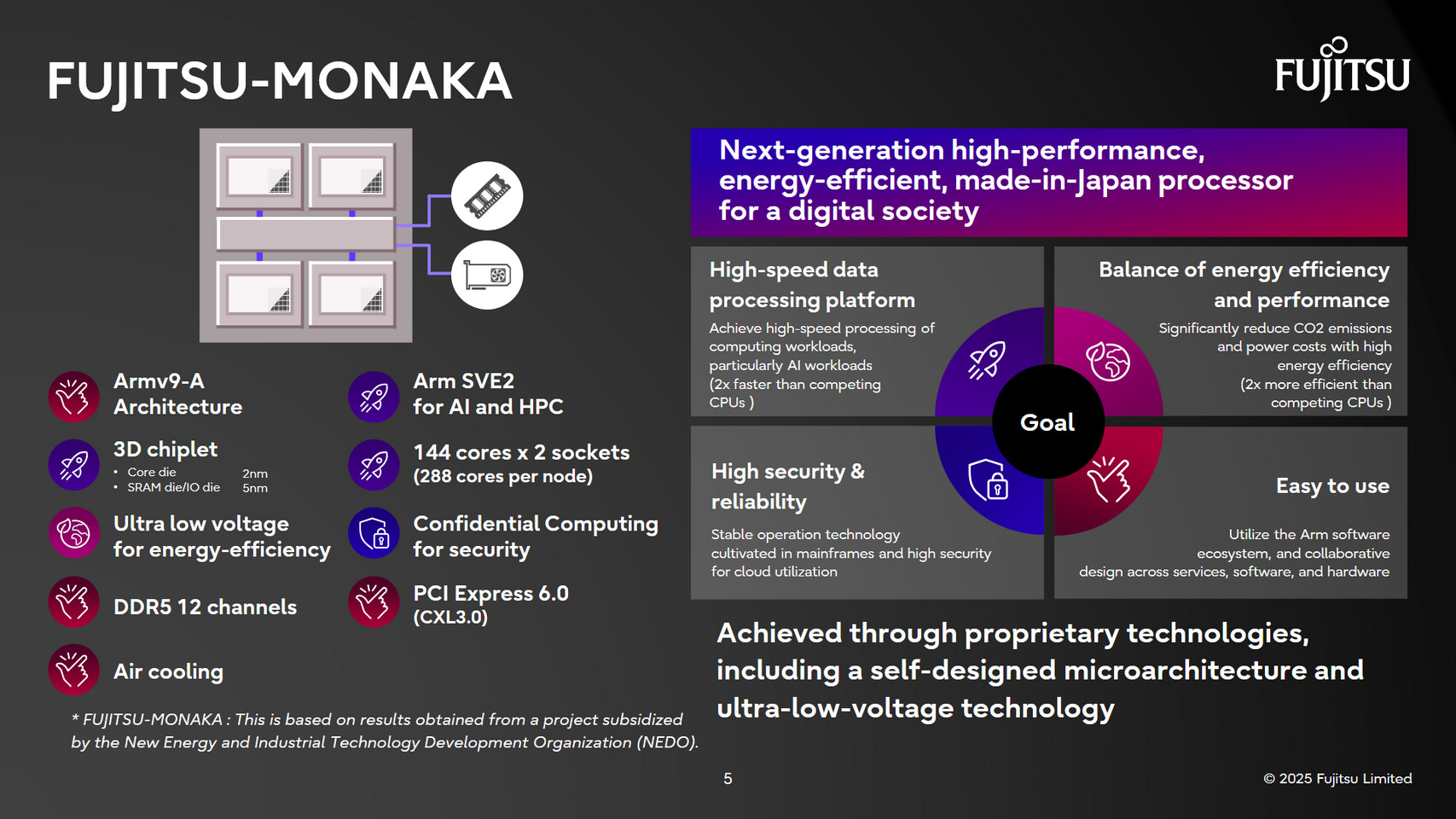

首款 Monaka 处理器基于 Armv9-A 指令集架构,采用 3D Chiplet 堆叠设计,将核心芯粒与独立的 SRAM 芯粒和 I/O 芯粒封装在同一封装内,每颗处理器集成 144 个 CPU 核心,通过双路配置可实现单节点最高 288 核心的规模。 平台支持 12 通道 DDR5 内存、PCIe 6.0 接口以及 CXL 3.0 互连,并配备 Arm SVE2 向量扩展,用于加速 AI 推理和高性能计算(HPC)等负载,富士通将其定位为高能效的数据中心处理器,面向 AI 推理、数值模拟和大规模数据处理等场景。

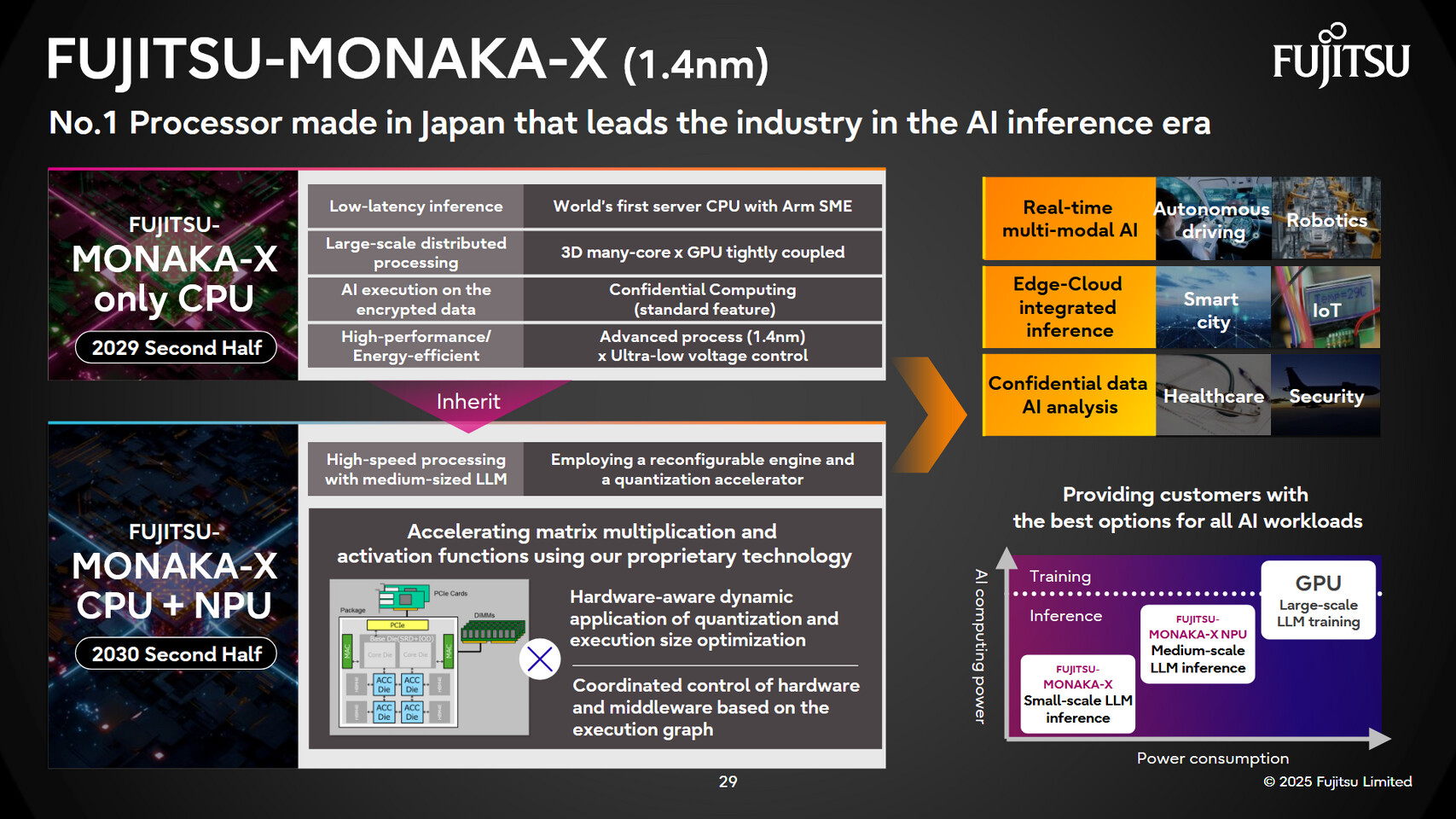

在此基础上,富士通规划了更加专用化的后续产品形态,路线图的下一个阶段是预计于 2029 年末推出的 Monaka-X,这是一款仅包含 CPU 的产品,将采用 1.4 nm 级制程工艺。 富士通表示,Monaka-X 将成为首款在服务器 CPU 上实现 Arm SME(可扩展矩阵扩展,Scalable Matrix Extension)的产品,旨在进一步增强矩阵运算能力以服务 AI 与 HPC 应用。 该处理器延续 3D 多芯片多核心布局,并强调与 GPU 的紧密耦合设计,同时将机密计算(confidential computing)相关的硬件安全能力作为标准配置集成到平台之中,以满足数据中心在安全隔离和隐私计算上的需求。

路线图的下一步是计划于 2030 年下半年推出的 “Monaka-X with NPU” 版本,此版本在 CPU 基础上加入封装内 NPU(神经网络处理单元),目标是针对中等规模大语言模型(LLM)等工作负载进行本地加速。 富士通正在探索在该平台中引入可重构计算引擎以及专用量化加速器,以更好地支持推理过程中对不同精度、不同模型结构的需求,并在能效与吞吐方面取得平衡。

按照既定路线,2031 年将迎来 Monaka-XX,这一代被描述为“完整的 CPU–NPU 融合芯片”,同样计划采用 1.4 nm 或更先进的制程节点,将通用计算与智能加速深度集成在一个平台上。 富士通通过这一系列产品迭代,意在在 Arm 服务器市场上进一步向高核心数、高能效方向推进,同时在架构层面持续增强原生 AI 加速能力,使 AI 推理与高性能计算能力成为数据中心平台的基础特性而非外挂选配。 整体路线图显示,富士通正借助新一代制程工艺、3D Chiplet 封装以及 Arm 生态扩展,在 2027–2031 年之间建立起一条从通用高效计算到深度 AI 融合的 Arm 服务器产品线。