随着人工智能 (AI) 工作负载日益庞大、复杂,用于处理所有数据的各种处理元件对功率的需求也空前高涨。然而,高效可靠地提供这种功率,同时又不损害信号完整性或引入热瓶颈,却带来了半导体历史上最严峻的设计和制造挑战。

与通用处理器不同,专为 AI 工作负载设计的芯片将密度推向极致。它们将更多晶体管封装到更小的空间内,同时增加晶体管的总数(通常以芯片的形式)。其结果是更大、更密集的系统级封装,其中电力传输不仅仅是一个电气问题,而是一个从单个芯片到服务器机架的封装、材料和系统集成挑战。

新思科技研究员Godwin Maben 表示:“功耗主要由动态功耗决定,而动态功耗主要受计算和内存之间数据移动的影响。例如,NVIDIA 的 Blackwell 功耗范围从 700 瓦到 1400 瓦。这使得高效的总线架构和架构创新(例如数据压缩策略)至关重要。”

由于内存和计算单元之间来回传输的数据量巨大,动态功耗占据主导地位。这些传输跨越庞大的内存层级结构,使用各种高速互连。但移动所有这些数据是有代价的,这会产生层层叠加的设计约束,从内存层级结构决策一直延伸到电源传输网络 (PDN)。

Imec研发副总裁Julien Ryckaert表示:“随着我们转向背面和3D堆叠,热量变得更加局部化,也更难消散。这种物理压缩加剧了电迁移和局部热点等挑战。”

为了使这些级别的电源传输易于处理,多学科设计团队必须全面思考电压调节的位置和方式、热量提取方式、材料在高电流应力下的行为,以及在电迁移和电压降影响可靠性之前,它们有多少裕度。这些设计决策的复杂性要求 EDA 工具、制造工艺和先进封装之间进行更紧密的耦合。

新思科技首席架构师 Jay Roy 表示:“如今,高性能计算和 AI 加速器已突破千瓦级界限。设计复杂性的爆炸式增长和周期的缩短给半导体 SOC 设计带来了持续的挑战。”

这种在最小化功耗的同时提升性能的追求,正迫使电力输送模型发生重大变革。这不再仅仅关乎降低电阻,而是关乎对电感行为、热梯度以及不同膨胀系数材料间耦合的建模。现在,对电压降、电流瓶颈和热点的早期预测至关重要,而且必须在实际布局和集成约束的背景下进行。

从横向到纵向供电

无论多少仿真都无法解决传统横向供电固有的局限性。在封装和印刷电路板上横向布线大电流电源走线会带来损耗和空间限制,而这些限制已经无法再扩展。当芯片功耗为 100 或 200 瓦时,这种方法尚可行,但现在却成了现代 AI 硬件的限制因素。

Saras Micro Devices 首席商务官 Eelco Bergman 表示:“目前的加速卡通常采用横向供电架构,将数千安培的电流通过长达数厘米的 PCB 走线,从电源模块传输到处理器。由于电流和走线电阻较大,这种方法会导致严重的功率损耗和过热。此外,用于支持不断增长的总功率、电源轨数量以及关键高速信号布线的电路板空间有限。”

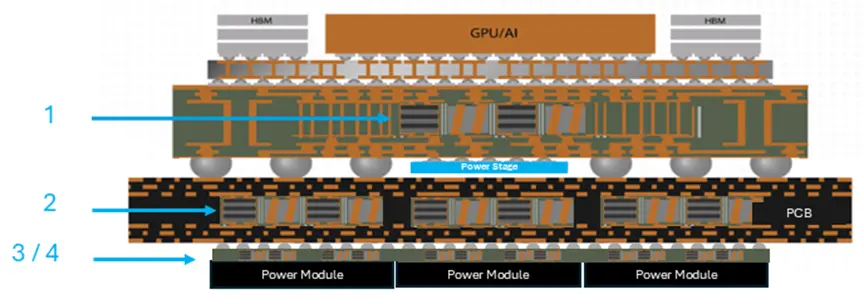

图 1:垂直供电网络,显示多域电容器模块直接嵌入封装基板

在这样的功率水平下,每毫欧姆的电阻都会转化为必须耗散的数瓦热量。此外,横向布线带来的空间限制常常需要在电源完整性和信号完整性之间做出权衡。在高带宽系统中,数百条高速SerDes通道与密集的电源层共享电路板空间,这种权衡变得难以维持。

为了克服这些限制,半导体行业正在积极探索垂直供电技术。通过将电源轨或稳压器直接嵌入芯片下方,并用低阻抗路径垂直连接,电源到硅片的距离可以显著缩短。这不仅降低了电压降和噪声,还释放了顶部布线空间,用于传输关键信号。

Bergman 补充道:“我们看到客户正在积极探索垂直供电架构,该架构采用嵌入式电压调节和集成电容解决方案,可以实现局部供电。这些方法可以释放顶部 PCB 空间,减少寄生损耗,并提高整体供电性能。”